Лекция №6

Тема: «Триггеры: устройство, разновидности, принцип работы»

Триггером называется устройство, имеющее два устойчивых состояния и сохраняющее любое из них сколь угодно долго после снятия внешнего воздействия, вызвавшего переход триггера из одного состояния в другое.

Поэтому говорят, что триггер обладает памятью. Триггер можно представить в общем случае состоящим из ячейки памяти и устройства управления (порой весьма сложного), преобразующего входную информацию в комбинацию сигналов, под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний.

По способу записи информации триггеры могут быть асинхронными и синхронными. Триггер называют асинхронным, если сам сигнал, несущий информацию, вызывает его переключение. В синхронных (тактируемых) триггерах информация записывается при одновременном воздействии информационного сигнала и синхронизирующего (разрешающего) импульса.

Синхронизация может осуществляться импульсом (потенциалом) или перепадом потенциала (фронтом или срезом импульса). В первом случае (статическое управление) сигналы на информационных входах оказывают влияние на состояние триггера в течение всего времени наличия синхроимпульса. Во втором случае (динамическое управление) воздействие информационных сигналов проявляется только в моменты изменения потенциала на входе синхронизации, т.е. при переходе его от 0 к 1 (фронт) или от 1 к 0 (срез).

По функциональному признаку различают RS-триггеры, D-триггеры, Т-триггеры и JK-триггеры, а также их комбинации.

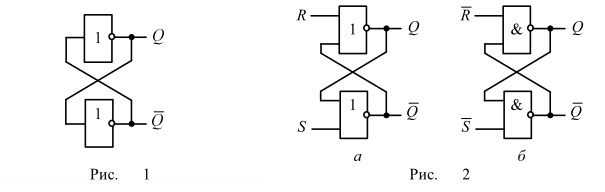

Основу любого триггерного устройства составляет элементарная ячейка памяти на двух инверторах с кольцом положительной обратной связи, называемая защелкой (рис. 1).

В асинхронном (нетактируемом) RS-триггере (рис. 2, а), выполненном на логических элементах ИЛИ-НЕ, состояниями описанной выше ячейки памяти можно управлять, подавая логическую 1 либо на вход 5 (Set) установки в состояние Q = 1, либо на вход R (Reset) сброса в состояние Q = 0. Если одновременно подать, а затем снять логическую 1 с обоих входов, то состояние триггера после снятия входных сигналов будет неопределенным. Такая комбинация на входах триггера является запрещенной. Минимальная длительность установочных импульсов должна вдвое превышать время задержки примененных логических элементов, чтобы по петле положительной обратной связи пришло подтверждение о фиксации нового состояния триггера.

Аналогичным образом работает асинхронный RS-триггер с инверсным управлением (рис. 2, б), выполненный на логических элементах И-НЕ. Установка триггера в единичное и нулевое состояние на выходе Q осуществляется подачей логического нуля на входы S или R. При единичных уровнях на обоих входах триггер не меняет своего состояния (находится в режиме хранения).

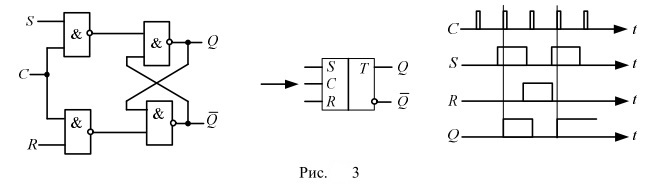

Тактируемый (синхронный) RS-триггер (рис. 3) может изменить свое состояние только с приходом тактового импульса на вход С. Помехи, действующие на информационных входах R и S между тактовыми импульсами, не влияют на работу триггера. Запрещенным является состояние CRS = 1.

При включении питания состояние триггера остается неопределенным.

После совпадения единичных уровней на входах S и С триггер устанавливается в единичное состояние. При совпадения логических единиц на входах R и С триггер сбрасывается в нулевое состояние.